## CPE/EE 422/522 Advanced Logic Design L13

Electrical and Computer Engineering University of Alabama in Huntsville

## **Additional Topics in VHDL**

- Attributes

- Transport and Inertial Delays

- Operator Overloading

- Multivalued Logic and Signal Resolution

- IEEE 1164 Standard Logic

- Generics

- · Generate Statements

- · Synthesis of VHDL Code

- Synthesis Examples

- · Files and Text IO

09/07/2003 UAH-CPE/EE 422/522 © AM

## Signal Attributes Attributes associated with signals that return a value Returns True if an event occurred during the current deta, else false STVENT True if a transaction occurred during the current delta, else false S'ACTIVE SLAST\_EVENT Time elapsed since the previous event on S SLAST VALUE Value of S before the previous event on S STAST\_ACTIVE Time elapsed since previous transaction on S A'event - true if a change in S has just occurred A'active - true if A has just been reevaluated, even if A does not change 09/07/2003 UAH-CPE/EE 422/522 © AM

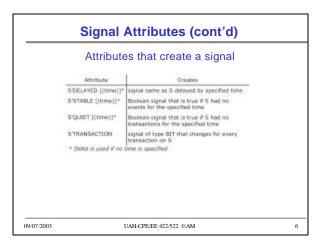

##

Signal Attributes (cont'd)

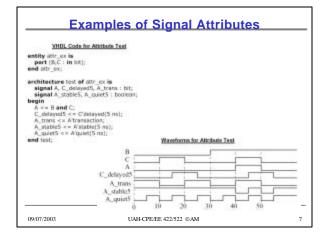

## Signal Attributes (cont'd) entity test is if (A'event) then Aev := '1'; else Aev := '0'; architecture bmtest of test is end if; if (A'active) then Aac := '1'; else Aac := '0'; signal A : bit; signal B : bit; end if; if (B'event) then Bev := '1'; else Bev := '0'; signal C : bit; A <= not A after 20 ns; end if; B <= '1'; else Bac := '0'; end if; $C \le A \text{ and } B;$ process(A, B, C) variable Aev : bit; if (C'event) then Cev := '1'; else Cev := '0'; variable Aac : bit; end if; if (C'active) then Cac := '1'; variable Bev : bit; variable Bac : bit; else Cac := '0'; variable Cev : bit; variable Cac : bit; end process; UAH-CPE/EE 422/522 @AM 09/07/2003

# check: process begin wait until rising\_edge(Clk); assert (D'stable(setup\_time)) report("Setup time violation") severity error; wait for hold\_time; assert (D'stable(hold\_time)) report("Hold time violation") severity error; end process check; UAH-CPEEE 422/522 ©AM 8

## **Assert Statement**

assert boolean-expression

report string-expression

severity severity-level

- If boolean expression is false display the string expression on the monitor

- · Severity levels: Note, Warning, Error, Failure

09/07/2003 UAH-CPE/EE 422/522 ©AM 9

### **Array Attributes** Type ROM is array (0 to 15, 7 downto 0) of bit; Signal ROM ( : ROM) Attribute Examples. Returns WLEFT(N) left bound of Nth index range SIMILEPT(1) = 0 SIMILEPT(2) = 7A'RECHTINO right bound of Nith Index range OMIRIGHT(1) = 15OMIRIGHT(2) = 0OM1HEGH(1) = 15 OM1HEGH(2) = 7 WHOSHOW) largest bound of Nth index range A'LOW(N) imatest bound of 4th index range OM110H(1) = 0 OM110H(2) = 0 A'RANGE(N) en index range OMITANGE(1) = 0 to 15 OMITANGE(2) = 7 downto ( ROM1REVERSE\_RANGE(1) = 15 dewnte 0 ROM1REVERSE\_RANGE(2) = 0 to 7 WREVERSE\_RANGE(N) Nth index range ROM3'LENGTH(1) = 16. ROM3'LENGTH(2) = 6 WILENGTHEND ios of Mth Index A can be either an array name or an array type. Array attributes work with signals, variables, and constants UAH-CPE/EE 422/522 © AM 10

# Procedure adds two n-bit bit, vectors and a carry and - requires an n-bit sym and a carry. Add1 and Add2 are assumed - to be of the same largift and dimensioned = 1 downto 0. precedure Addrect (Add1,Add2: In bit, vector) (Circ in bit; signal Sum: out bit, vector) signal Sum: out bit, vector; signal Sum: out bit, vector; signal Sum: out bit, vector; signal Cost; out bit; n:in postive) is variable C: bit; begin C:= 0; for i in 0 to n-1 loop Sum(i) <= Add1(i) see Add2(i) see C; C:= (Add1(i) and Add2(ii) or (Add1(i) and C) or (Add2(i) and C); and sloop; Cost <= C; end Addrect; Note: Add1 and Add2 vectors must be dimensioned as N-1 downto 0. Use attributes to write more general procedure that places no restrictions on the range of vectors other than the lengths must be same.

```

Procedure for Adding Bit Vectors

-- This procedure adds two bit, vectors and a carry and returns a sum

-- and a carry. Both bit, vectors should be of the same length.

procedure Addivec?

(Add3,Add2: in bit, vector;

Cits: in bit;

signal Sum: out bit, vector;

signal Sum: out bit lis

variable Citit = City and bit;

allas not bit, vector(Add3) length-1 dewate 0) is Add1;

allas not bit, vector(Add3) length-1 dewate 0) is Add1;

allas not bit, vector(Add3) length-1 dewate 0) is Add2;

allas not bit, vector(Add3) length-1 dewate 0) is Add2;

allas not bit, vector(Add3) length-1 dewate 0) is Add2;

allas not live, vector (Add3) length-1 dewate 0) is Add2;

allas not live, vector (Add3) length-1 dewate 0) is Add2;

allas not live, vector (Add3) length-1 dewate 0) is Add2;

allas not live, vector (Add3) length-1 dewate 0) is Add2;

allas not live, vector (Add3) length-1 dewate 0) is Add2;

allas not live, vector (Add3) length-1 dewate 0) is Add2;

allas not live, vector (Add3) length-1 dewate 0) is Add1;

allas not live, vector (Add3) length-1 dewate 0) is Add1;

allas not live, vector (Add3) length-1 dewate 0) is Add1;

allas not live, vector (Add3) length-1 dewate 0) is Add1;

allas not live, vector (Add3) length-1 dewate 0) is Add1;

allas not live, vector (Add3) length-1 dewate 0) is Add1;

allas not live, vector (Add3) length-1 dewate 0) is Add1;

allas not live, vector (Add3) length-1 dewate 0) is Add1;

allas not live, vector (Add3) length-1 dewate 0) is Add1;

allas not live, vector (Add3) length-1 dewate 0) is Add1;

allas not live, vector (Add3) length-1 dewate 0) is Add1;

allas not live, vector (Add3) length-1 dewate 0) is Add1;

allas not live, vector (Add3) length-1 dewate 0) is Add1;

allas not live, vector (Add3) length-1 dewate 0) is Add1;

allas not live, vector (Add3) length-1 dewate 0) is Add1;

allas not live, vector (Add3) length-1 dewate 0) is Add1;

allas not live, vector (Add3) length-1 dewate 0) is Add1;

allas not live, vector (Add3) length-1 dewate 0) is Add1;

allas not live, vector (Add3) length-1 dewate 0) is Add1;

a

```

```

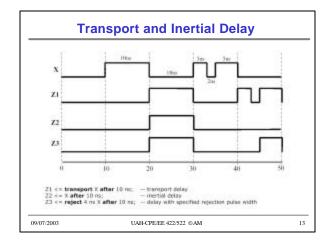

Transport and Inertial Delay (cont'd)

Z3 <= reject 4 ns X after 10 ns;

Reject is equivalent to a combination of inertial and transport delay:

Zm <= X after 4 ns;

Z3 <= transport Zm after 6 ns;

Statements executed at time T

- B at T+1. C at T+2

A <= transport B after 1 ns;

A <= transport C after 2 ns;

Statements executed at time T

Statements executed at time T

-C at T + 1:

-C at T + 2:

A <= B after 1 ns;

A <= transport B after 2 ns;

A <= C after 2 ns;

A <= transport C after 1 ns;

UAH-CPE/EE 422/522 ©AM

```

## Operator Overloading

- Operators +, operate on integers

- Write procedures for bit vector addition/subtraction

addvec, subvec

- Operator overloading allows using + operator to implicitly call an appropriate addition function

- · How does it work?

- When compiler encounters a function declaration in which the function name is an operator enclosed in double quotes, the compiler treats the function as an operator overloading ("+")

- when a "+" operator is encountered, the compiler automatically checks the types of operands and calls appropriate functions

09/07/2003 UAH-CPE/EE 422/522 ©AM 15

## VHDL Package with Overloaded Operators -- This pedage provides two overloaded functions for the plus operator sectage bit persisted is functionally to persisted in the persistent pe

## **Overloaded Operators**

- A, B, C bit vectors

- A <= B + C + 3 ?

- A <= 3 + B + C ?

- · Overloading can also be applied to procedures and functions

- procedures have the same name type of the actual parameters in the procedure call determines which version of the procedure is called

09/07/2003

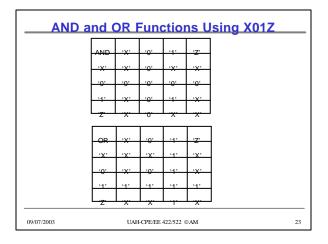

## **Multivalued Logic**

- Bit (0, 1)

- Tristate buffers and buses => high impedance state 'Z'

- Unknown state 'X'

- e. g., a gate is driven by 'Z', output is unknown

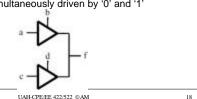

- a signal is simultaneously driven by '0' and '1'

## **Tristate Buffers** se WORK fourpook.all; stity t\_buff\_semplie port (s,b,t,d : is X002; — signals are f: out X002); — 4 saleed ed L,buff\_carep; hitecture t\_buff\_conc of t\_buff\_complies f <= 5 when b = '1' else '2'; f <= c when d = '1' else '2'; end t\_belf\_cooc; rchitecture t\_buf\_blw of t\_buf\_compl is gin buff1: process (s,b) of (b='1') then f<=a; else $\frac{d \log (2^n)}{d \log (2^n)} = -\frac{d \log (n)}{d \log (n)}$ when not enabled and if; and process buff? ; Resolution function to determine the actual value of f since it is buff2: process $(c_id)$ begin if $(d^{-1})$ then $f_i = c_i$ when $f_i = c_i$ is $(d^{-1})$ then $f_i = c_i$ with a cuput high Z when not enabled and if: driven from two different sources cess buff2: 09/07/2003 UAH-CPE/EE 422/522 @AM 19

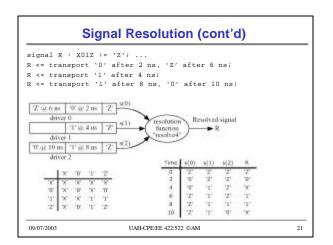

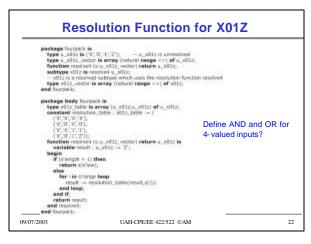

## Signal Resolution

- · VHDL signals may either be resolved or unresolved

- · Resolved signals have an associated resolution function

- Bit type is unresolved

- there is no resolution function

- if you drive a bit signal to two different values in two concurrent statements, the compiler will generate an error

09/07/2003

UAH-CPE/EE 422/522 © AM

20

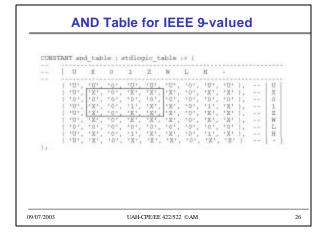

## IEEE 1164 Standard Logic · 9-valued logic system - 'U' - Uninitialized - 'X' - Forcing Unknown - '0' - Forcing 0 If forcing and weak signal are - '1' - Forcing 1 tied together, the forcing signal dominates. - 'Z' - High impedance - 'W' - Weak unknown Useful in modeling the internal - 'L' - Weak 0 operation of certain types of - 'H' - Weak 1 ICs. - '-' - Don't care In this course we use a subset of the IEEE values: X10Z 09/07/2003 UAH-CPE/EE 422/522 ©AM 24

##

## Function "and" [1 | sot\_wing(c) r | std\_wing(c) return UNDL is begin return (and\_table(), r)]; and "and"; function "and" [ ( | r | sts\_logic\_vector | return std\_logic\_vector is alias in | std\_logic\_vector (1 to FLENGTH ) is () alias in | std\_logic\_vector (1 to FLENGTH ) is r; variable result | sd\_logic\_vector (1 to FLENGTH ) is r; variable result | sd\_logic\_vector (1 to FLENGTH ); begin if ( TLENGTH /= rLENGTH) then assert FALSE report "Angurands of overloaded 'and' operator are not of the same length" severity FALURE; also for | in result\*RANGE loop result() | end\_table (M(I), re|I)); end loog; and d); return result; end "and") UAH-CPE/EE 422/522 @AM 27

## <u>Generics</u>

- Used to specify parameters for a component in such a way that the parameter values must be specified when the component is instantiated

- · Example: rise/fall time modeling

```

entity NAND2 is generic (Tits). Tall: time; bad: natural(): perf (ab.) in bit; ci out bit); and NAND2; and NAND2; and NAND2; signal nand_value: bit; bit; bigin nand_value: a nand b; c = nand_value = nand b; c = nand_value = nand b; d = nand_value = nan

```

09/07/2003 UAH-CPE/EE 422/522 ©AM 28

# Rise/Fall Time Modeling Using Generics entity MARD2 is: generic (Tings, Tbill) brine; load insturely; gent (a,b) in bit; client bit); end in MDD2; end in MDD2; end in MDD2 is: mignal rand, value : bit; begin reset who after Thise + 3 ris \* bod) when rand, value = '2' enter rand, value after (Thill + 2 ris \* lead); end behavior: entity NAFD2, past is poet (ini, ind, ind, ind ish bit) out(i, out2) out bit); end MARD2 (bit); end MARD2 (bit) creates the Delivers of NAFD2 (bit) is comparers (Thise librace of NAFD2 (bit); end MARD2 (bit); end (a,b) ish bit; c. out bit); end iii NAFD2 (percent map (2 ris, 1 ris, 2) port map (ini, ini2, out1); end iii NAFD2 (percent map (2 ris, 1 ris, 2) port map (ini, ini2, out1); end iii NAFD2 (percent map (2 ris, 1 ris, 2) port map (ini, ini2, out1); end

## **Generate Statements** · Provides an easy way of instantiating components when we have an iterative array of identical components • Example: 4-bit RCA Full C(3) C(2) Full Full Adder A(3) B(3) A(2) B(2) A(1) B(1) A(0) 09/07/2003 UAH-CPE/EE 422/522 © AM 30

## 4-bit Adder entity Adder4 is port (A, B: in bit\_vector(3 downto 0); Ci: in bit; S: out bit\_vector(3 downto 0); Co: out bit); -- Inputs -- Outputs end Adder4; architecture Structure of Adder4 is component FullAdder port (X, Y, Cin: in bit; Cout, Sum; out bit); -- Inputs -- Outputs end component; signal C: bit\_vector(3 downto 1); begin —instantiate four copies of the FullAdder FA0: FullAdder port map (A(0), B(0), Cl, C(1), S(0)); FA1: FullAdder port map (A(1), B(1), C(1), C(2), S(1)); FA2: FullAdder port map (A(2), B(2), C(2), C(3), S(2)); FA3: FullAdder port map (A(3), B(3), C(3), Co, S(3)); end Structure; 09/07/2003 UAH-CPE/EE 422/522 ©AM 31

## Synthesis of VHDL Code

- Synthesizer

- take a VHDL code as an input

- synthesize the logic: output may be a logic schematic with an associated wirelist

- Synthesizers accept a subset of VHDL as input

- Efficient implementation?

- Context

. . .

A <= B and C; wait until clk'event and clk = `1';

A <= B and C;

Implies CM for A Implies a register or flip-flop

09/07/2003 UAH-CPE/EE 422/522 ©AM

## Synthesis of VHDL Code (cont'd)

- When use integers specify the range

if not specified, the synthesizer may infer 32-bit register

- When integer range is specified, most synthesizers will implement integer addition and subtraction using binary adders with appropriate number of bits

- General rule: when a signal is assigned a value, it will hold that value until it is assigned new value

09/07/2003 UAH-CPE/EE 422/522 ©AM 34

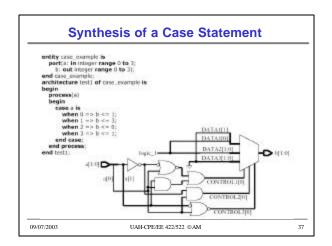

# Unintentional Latch Creation entity latch example as pertion is integer range 0 to 3; b) out bit? end latch example; architecture tests of texth, example is bagin process(s) begin case a lin when 0 => b <= 1; when 1 >> b <= 0; when 2 >> b <= 1; when 2 >> b <= 1

# if A = '1' then NextState <= 3; end if; What if A /= 1? Retain the previous value for NextState? Synthesizer might interpret this to mean that NextState is unknown! if A = '1' then NextState <= 3; else NextState <= 2; end if; 09/07/2003 UAH-CPEÆE 422/522 @AM 36</pre>

## Standard VHDL Synthesis Package

- Every VHDL synthesis tool provides its own package of functions for operations commonly used in hardware models

- IEEE is developing a standard synthesis package, which includes functions for arithmetic operations on bit\_vectors and std\_logic vectors

- numeric\_bit package defines operations on bit\_vectors

- type unsigned is array (natural range<>) of bit;

- type signed is array (natural range<>) of bit;

- package include overloaded versions of arithmetic, relational, logical, and shifting operations, and conversion functions

- numeric\_std package defines similar operations on std\_logic vectors

09/07/2003 UAH-CPE/EE 422/522 ©AM 40

## Numeric\_bit, Numeric\_std

- · Overloaded operators

- Unary: abs, -

- Arithmetic: +, -, \*, /, rem, mod

- Relational: >, <, >=, <=, =, /=

- Logical: not, and, or, nand, nor, xor, xnor

- Shifting: shift\_left, shift\_right, rotate\_left, rotate\_right, sll, srl, rol, ror

09/07/2003

UAH-CPE/EE 422/522 © AM

## Numeric\_bit, Numeric\_std (cont'd)

If the left and right signed operands are of different lengths, the shortest operand will be sign-extended before performing an antimetic operation. For unsigned operands, the shortest operand will be extended by filling in 0's on the left. Examples:

```

signed: "01181" + "1011" Decomes "01101" + "11011" = "01000" unsigned: "01181" + "1011" becomes "01101" + "01011" = "11000"

```

When addition is performed on unsigned or signed operands, the final carry is discarded and overflow is ignored. If a carry is needed, an extra bit can be added to one of the operands. Examples:

09/07/2003

41

43

UAH-CPE/EE 422/522 ©AM

42

## Numeric\_bit, Numeric\_std (cont'd)

09/07/2003

UAH-CPE/EE 422/522 @AM

## Synthesis Examples (1)

09/07/2003 UAH-CPE/EE 422/522 © AM

•11